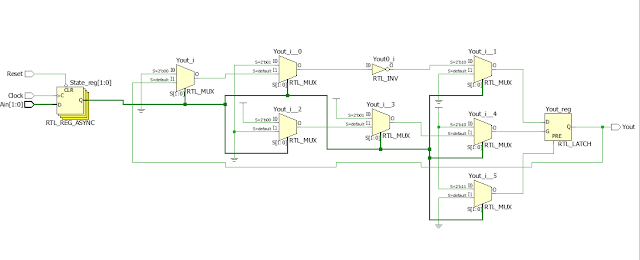

module Variety_sequence_detect(Ain,Yout,Clock,Reset);

input Clock,Reset;

input [1:0] Ain;

output reg Yout;

reg [1:0] State;

parameter S0=2'b00,

S1=2'b01,

S2=2'b10, //toggle state

S3=2'b11; //Led on

always @(posedge Clock,posedge Reset)

begin

if (!Reset)

State<= S0;

else case(Ain)

S0: if (Ain==0 ) State<=S0; else if(Ain==1) State<=S1; else if(Ain==2) State<=S2; else if(Ain==3 ) State<=S3;

S1: if (Ain==1 ) State<=S1; else if(Ain==2) State<=S2; else if(Ain==3) State<=S3; else if(Ain==00 ) State<=S0;

S2: if (Ain==2 ) State<=S2; else if(Ain==1) State<=S1; else if(Ain==3) State<=S3; else if(Ain==0 ) State<=S0;

S3: if (Ain==3 ) State<=S3; else if(Ain==1) State<=S1; else if(Ain==2) State<=S2; else if(Ain==0 ) State<=S0;

endcase

always @(State)

begin

if (State==S0) Yout=1'b0;

if (State==S1) Yout=1'b0;

if (State==S2) Yout=~Yout;

if (State==S3) Yout=1;

end

endmodule

No comments:

Post a Comment